Современные системы цифровой обработки сигналов широко используют высокопроизводительные процессоры цифровой обработки сигналов (ВПЦОС). Аппаратура на их основе используется при обработке радиолокационной информации, изображений в реальном времени, цифровой обработке речевых сигналов, в системах радиосвязи, системах дистанционного зондирования атмосферы, цифровой измерительной аппаратуре, находит широкое применение в системах управления транспортными, авиационно-космическими и энергетическими комплексами.

В данной работе рассматривается реализация на высокопроизводительном процессоре цифровой обработки сигналов (ВПЦОС), разработанном АО «ПКК Миландр» [1], рангового алгоритма обнаружения, широко используемого при решении задач порогового обнаружения [2]. Производится сравнение полученных результатов с результатами реализации алгоритма на процессоре ADSP-TS201 TigerSHARC фирмы Analog Devices [3,4].

Алгоритм порогового обнаружения методом порядковых статистик (ранговый алгоритм) состоит из нескольких этапов. На первом этапе входные данные подвергаются преобразованию

![]()

![]() ,

,

где x(n) – n-й отсчет входных данных, 0<n<N,

y(r) – r-й отсчет преобразованных данных, 0<r<R,

D – порядок максимизации, D=N/R.

На следующем этапе формируется порог обнаружения посредством скользящего окна размером M, при этом внутри окна производится упорядочивание данных согласно условию y(r-M/2)≤ y(r-M/2+1)≤… y(r+M/2-1). После упорядочивания отсчетов данных в текущем окне выбирается статистика с номером L и умножается на пороговый коэффициент k, значение которого выбирается исходя из заданной вероятности ложной тревоги.

На последнем этапе производится сравнение входных данных с отсчетами вычисленного порога, в результате чего формируется массив признаков превышения порога.

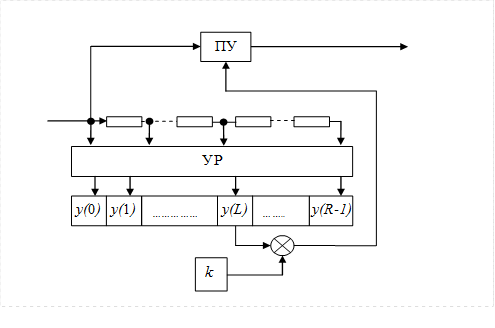

Структурная схема рангового обнаружителя показана на рисунке 1.

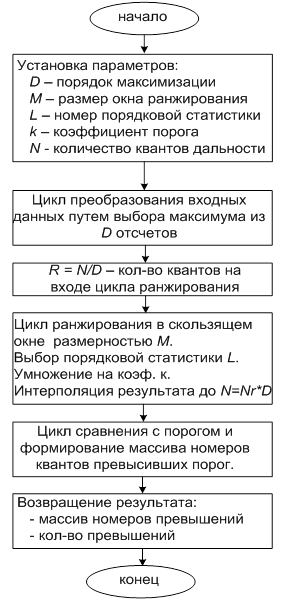

Алгоритм был реализован в виде программного модуля на языке ассемблера. На рисунке 2 показана блок-схема алгоритма, реализующего ранговое обнаружение.

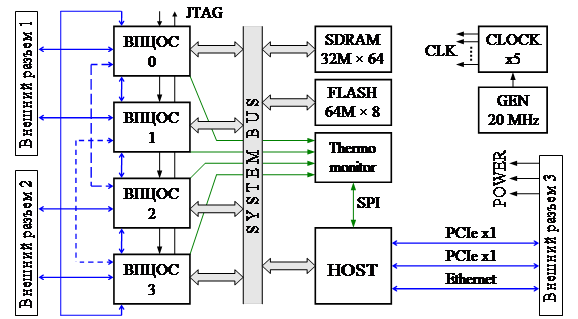

Для апробации алгоритма использовался многопроцессорный (интегрированный) модуль (ИМ) на ВПЦОС АО «ПКК Миландр», разработанный на кафедре информационных радиосистем Нижегородского государственного технического университета им. Р.Е. Алексеева [5]. Структура ИМ показана на рисунке 3.

Рис.1. Структурная схема рангового обнаружителя

Здесь: ПУ – пороговое устройство; УР – устройство ранжирования

В состав модуля входят:

- четыре процессора обработки сигналов ВПЦОС0 – ВПЦОС3;

- блок синхронной динамической памяти SDRAM объемом 256МБайт;

- постоянное запоминающее устройство FLASH объемом 64МБайта;

- контроллер системной шины (HOST), выполненный на базе микросхемы FPGA Virtex-6 фирмы Xilinx XC6VLX130T;

- температурный монитор Thermo monitor на базе двух микросхем TMP422 (или TMP423) фирмы Texas Instruments;

- опорный генератор синхронизации GEN с частотой 20МГц;

- умножитель на 5 частоты опорного генератора CLOCKx5.

Рис.2. Блок-схема алгоритма рангового обнаружения

Рис. 3. Структура ИМ

Процессоры ВПЦОС, динамическая память, постоянная память и контроллер подключены к системной шине кластера SYSTEM BUS разрядностью данных 64 бита. Два LINK-порта каждого процессора используются для организации кольцевой связи (сплошные линии на рисунке 1) и по одному – для организации возможных перекрестных связей (штриховые линии на рисунке 1). По одному LINK-порту каждого процессора выводится на внешние разъемы. HOST-контроллер обеспечивает доступ к системной шине процессорного кластера через внешние интерфейсы Ethernet и PCI-Express.

Сигнальный процессор, использованный в ИМ, имеет следующие характеристики:

· Тактовая частота ядра – до 500 МГц;

· Объем встроенной статической памяти – 24 Мбит;

· Пиковая производительность – 3000 MFLOP;

· Разрядность внешней шины – 64 бит;

· Пропускная способность внутренней памяти – 25,2 ГБайт/с;

· Пропускная способность внешней шины – 800 МБайт/с;

· Количество внешних последовательных портов – 4;

· Пропускная способность внешнего последовательного порта – 1 ГБайт/с;

· Полное соответствие при выполнении инструкций аналогу – процессору фирмы Analog Devices ADSP-TS201S TigerSHARC (2 АЛУ с плавающей точкой);

· 14 канальный контроллер прямого доступа к памяти;

· Встроенный арбитр мультипроцессорной шины, исключающий конфликты шины.

В таблице 1 приведены результаты выполнения программы на ВПЦОС. Для сравнения в той же таблице показаны результаты, полученные при реализации указанного алгоритма на процессоре TigerSHARC ADSP-TS201 в составе модуля ЦОС ADSP-TS201S EZ-KIT Lite.

Таблица 1

Результаты исполнения алгоритма

|

Размер окна, M |

Машинных тактов процессора на 1 отсчет входных данных, D=3, N=200 |

|

|

ВПЦОС АО «ПКК Миландр» |

TigerSHARC ADSP-TS201 |

|

|

7 |

43 |

44 |

|

15 |

60 |

60 |

|

23 |

77 |

75 |

|

31 |

93 |

90 |

При реализации алгоритмов были использованы:

· Встроенные счетчики циклов;

· Чтение и запись квадрословами;

· Постинкрементация, арифметические и логические операции с указателями;

· Встроенная адресация циклических буферов;

· Условные отложенные переходы с предсказанием и без предсказания ветвления;

· Безусловные отложенные переходы;

· Исполнение нескольких команд за один такт;

· Пересылка регистров через АЛУ.

Анализ данных, приведенных в таблице, показывает, что при всех размерах М окна ранжирования число машинных тактов процессора и время выполнения алгоритма на процессоре ВПЦОС АО «ПКК Миландр» было практически таким же, как и время, затрачиваемое на процессоре TigerSHARC ADSP-TS201 фирмы Analog Devices.

Сравнительный анализ результатов реализации алгоритма порогового обнаружения методом порядковых статистик, в основе которого лежит задача сортировки входных данных, на процессоре TigerSHARC ADSP-TS201 фирмы Analog Devices и ВПЦОС российской компании АО «ПКК Миландр» показал, что при реализации данного алгоритма скорость вычислений ВПЦОС АО «ПКК Миландр» практически совпадает со скоростью вычислений процессора TigerSHARC ADSP-TS201S.

Это позволяет утверждать, что разработанный отечественный сигнальный процессор не уступает по характеристикам сигнальному процессору TigerSHARC ADSP-TS201S и позволяет обеспечить решение практически важных задач цифровой обработки сигналов, в частности, задач радиолокационного обнаружения.

Работа выполнена при поддержке Министерства образования и науки РФ в рамках договора № 02.G25.31.0061 от «12» февраля 2013 года (в соответствии с Постановлением Правительства Российской Федерации от 9 апреля 2010 г. №218).

Рецензенты:

Хранилов В.П., д.т.н., профессор кафедры компьютерных технологий в проектировании и производстве Нижегородского государственного технического университета имени Р.Е. Алексеева, г. Нижний Новгород;

Есипенко В.И., д.ф.-м.н., профессор кафедры «Электроника и сети ЭВМ» Нижегородского государственного технического университета имени Р.Е. Алексеева, г. Нижний Новгород.