Введение

Программируемые логические интегральные схемы (ПЛИС) имеют широкое применение в электронике. Главной составной частью ПЛИС являются функциональные блоки (ФБ), позволяющие аппаратно выполнять сконфигурированные разработчиком функции. ФБ занимают основную площадь кристалла ПЛИС, поэтому уменьшение площади ФБ – одна из основных проблем построения ПЛИС. Также у большинства существующих на сегодня ПЛИС (за исключением достаточно дорогого класса микросхем с flash-памятью) память конфигурации является энергозависимой, что не всегда удобно в применении при заданном соотношении цены и качества.

Решение данных проблем может заключаться в использовании относительно новой элементной базы в функциональных преобразователях (ФП, в терминологии фирмы Altera – Look-Up Table – LUT [5]) или в общем случае – в энергонезависимой памяти конфигурации. Нами предлагаются способы интеграции традиционных КМОП ФБ с элементной базой на основе мемристорных элементов [2, 4].

Метод формирования функциональных блоков

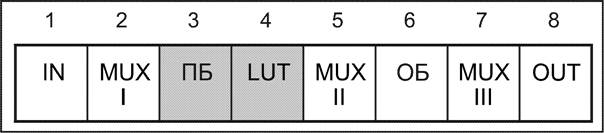

В традиционную структуру ФБ введем специальный программирующий блок (ПБ) и заменим схемотехнику LUT для поддержки мемристорной элементной базы. Разделим ФБ на условные части (рис.1), которые будем рассматривать выборочно.

Рисунок 1 – Компоненты функционального блока на базе мемристоров

ФБ состоит из блока входных терминалов (IN), ряда мультиплексоров (MUX I), позволяющих гибко коммутировать входные сигналы с LUT, программирующего блока для обслуживания LUT, мультиплексоров (MUX II), коммутирующих выходные сигналы LUT с блоками, выполняющими вычисления, малого операционного блока (ОБ), выполняющего простейшую операцию, например, только суммирование, а также выходных мультиплексоров (MUX III)и терминалов (OUT).

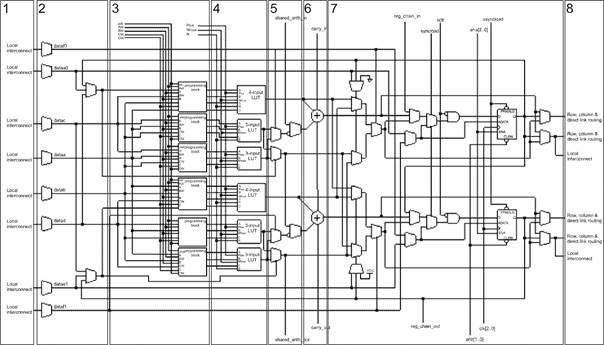

Предлагается для реализации данной структуры ФБ в качестве примера взять за основу известные ФБ ПЛИС семейства Stratix II фирмы Altera [3] и модернизировать их для использования LUT с мемристорами. Добавление программирующего блока и изменение внутренней структуры LUT даст ряд преимуществ, о которых написано выше. Таким образом, схемотехника ФБ с наличием всех компонентов из рис. 1 будет выглядеть так, как показано на рис. 2.

Рисунок 2 – Модернизированный функциональный блок ПЛИС Stratix II фирмы Altera для использования мемристоной элементной базы (выделенные области: 1) входные терминалы, 2) блок MUX I, 3) программирующий блок 4) LUT, 5) блок MUX II, 6) операционный блок, 7) блок MUX II, 8) выходные терминалы)

Наличие большого количества мультиплексоров позволяет легко изменять логическую структуру ФБ (отключать часть схемы либо направлять сигналы на необходимые вычислительные блоки). Для этого в первую очередь необходимо задать логику работы ФБ, в соответствии с которой конфигурируются все блоки мультиплексоров, например, вывод данных может быть синхронным или асинхронным, результат вычисления двух логических функций суммируется или выводится по отдельности.

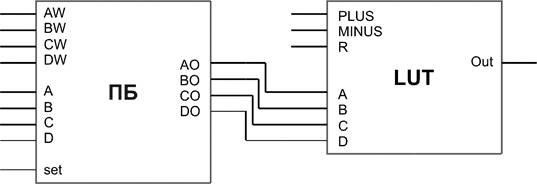

После конфигурирования коммутирующей структуры ФБ необходимо произвести «программирование» элементов памяти в LUT (рис. 3). Особенности внутренней организации и схемотехники LUT описаны нами ранее в статье [1].

В блоке LUT присутствует 4-хразрядный дешифратор (DC), формирующий адрес обращения к одной из 16-ти ячеек памяти, а также блоки для преобразования уровней напряжений (согласование необходимо в связи с тем, что LUT из [1] рассчитан на оперирование с логическими уровнями от +5 до -5 В).

Рисунок 3 – Внутренняя структура LUT

Для выполнения операции конфигурирования данного LUT в ФБ введен вспомогательный блок программирования, позволяющий переключать LUT в режимы записи конфигурации и чтения записанных данных (рис. 4).

Рисунок 4 – Подключение программирующего блока к LUT

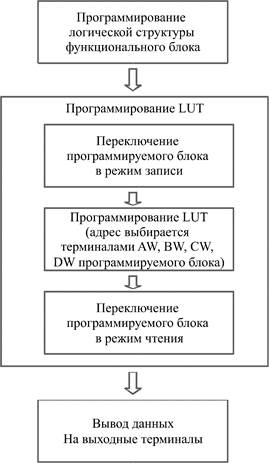

Алгоритм конфигурирования

Алгоритм использования предложенной структуры ФБ показан на рис. 5. Конфигурирование начинается после подачи на терминал set (см. рис. 4) логической единицы, которая переводит программирующий блок в режим записи данных в LUT. Далее последовательно перебираются адреса (терминалами AW, BW, CW, DW) ячеек LUT и подается активный уровень на терминалы PLUS или MINUS. После режима «программирования» на терминале set устанавливается логический ноль, переключая программирующий блок в режим чтения.

Для считывания данных из произвольной ячейки задается адрес на входных терминалах A, B, C, D программирующего блока и подается логическую единицу на терминал R блока LUT.

Рисунок 5 – Маршрут программирования функциональных блоков ПЛИС на основе мемристоров

На основе предложенного метода разработана модель ФБ, которая была промоделирована в САПР Cadence. Анализ полученных временных диаграмм показал ее полную работоспособность.

Функциональные блоки ПЛИС, построенные с использованием мемристорных элементов, имеют сложную разветвленную структуру, позволяющую гибко программировать блок практически под любую задачу.

Описанный метод позволяет разрабатывать ФБ ПЛИС на основе мемристоров, что дает возможность существенно уменьшить площадь, занимаемую LUT, так как ячейки памяти на основе мемристоров в 20-25 раз меньше по площади ячеек памяти на транзисторах. Представленный алгоритм можно использовать практически для любого ФБ, заменив LUT из оригинальной схемы на связку ПБ с LUT, описанную в данной статье.

Рецензенты:

Агеев О.А., д.т.н., профессор, декан факультета электроники и приборостроения Южного федерального университета, г. Таганрог.

Рындин Е.А., д.т.н., профессор, профессор кафедры конструирования электронных средств Южного федерального университета, г. Таганрог.